DDR3 Routing - Simplified Part 1

Part two of this series covers net length measurements and methods to ensure your matched length routes are properly implemented in Altium.

We will also look at a script 'Fix Connections' which is a modification of 'Fix Overlaps' that Petar Perisin created.

Before we dive into using the 'Fix Connections' script, we will look at the accuracy of net length measurements in Altium.

Altium Net Length Bugs - Fact or Fiction

Have you heard that Altium has net length bugs ?

Or that the 'From-To' data in the PCB panel is not accurate ?

I have seen messages on forums and blogs that claim Altium has bugs when it comes to extracting accurate net length data from the PcbDoc.

I created a test case to prove if these reported bugs were fact or fiction.

Starting with a simple schematic which has three test point pads connected to the same net named "DDR_D1".

Defined a simple 4 layer stack up and ported the schematic to the pcb.

To simplify the math involved to check the accuracy of measured and reported net lengths the grid was set to 100 mil.

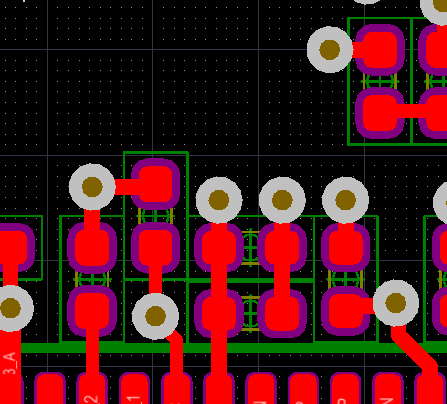

The design is displayed using the 2D transparent mode to allow for visual inspections of the routes.

With the Origin at the center of pad "A" as shown below.

As shown above I'm starting with all routes on the top layer.

Since the three pads A,B,C are all on a 100 mil grid we know these lengths are:

A to the intersection = 400 mils

A to B is 400 + 300 = 700

A to C is 400 + 200 = 600

B to C 500

With origin set at the center of pad "A" it is a simple matter of double clicking on any of the three trace segments to bring up the properties dialog and verify the track lengths.

One popular way to get accurate track length data in Altium is to select one or more track segments and press "R" then "S" on the keyboard to display the length of the selected track segments.

As shown below I have selected two of three segments and pressed the "R" then "S" key.

I am confident that Altium has reported this length correctly.

It would you be nice to be able to grab this measured data. Example press a command button to copy the measurement to your clipboard.

I submitted a feature request ( New Idea # 3279 ) to Altium, however it has not received much support.

Idea 3279

If you like this idea click on the above link and cast your vote.

Next we will use the PCB panel to examine the net lengths.

As shown above in the PCB panel the total length of the "DDR_D1" net is 900 mils, which is exactly correct.

Next we will examine the lengths between A,B,C using the From-To Editor

As shown above I selected in the second pane A-1 and B-1, then I added this selection to the 3rd (lower) pane. As shown the A-1 to B-1 is 700 mils. Again I'm confident this is correct.

Now let's make things a little more interesting.

I will drop a via at the intersection of A,B,C and move each of the three segments to different layers, then check the results. Again I'm sure the results are correct.

Note that the measurements (AD13.3) do not take into account the via length as we transition from one layer to another.

Regarding these layer transition lengths through the vias which are minimal. It is up to you to determine if the via lengths are critical to the overall length of the nets in your project.

Tip:

If you use the same number of vias and the same layers to route a data lane then the vias do not need to be accounted for.

Bad Connections

Next I will demonstrate how to get the reported bugs (bad length results).

I will change the grid from 100 to 1 mil and pull back the track on the top layer.

As show above I have pulled the track on the top layer a bit to the left so that is not centered in the pad at the 3-way intersection..

As show below we are now getting 688 vice 700 mil for the A to B path.

If I also pull the 'B' track the from the center of the intersection I can get a From-To length of 677 vice 700.

Your net length results will vary depending on how many bad connections are in the net.

Let's look at what has happened to the total net length. It is reporting 888 which is correct for total routed length of the tracks.

Note that the design will pass DRC checks for opens, because the tracks are contacting the pads.

Where are these reported bugs ?

"we have met the enemy and he is us"

Altium is reporting the actual routed track lengths.

If you need accurate length data then route your tracks accordingly.

Fix Connections Script

Download Script Link:

Using this script we can quickly identify where the bad connections are and correct them.

With the tolerance set for 0.1 mil, select OK.

As shown below the script has found and highlighted the bad connection.

Conclusion:

Yes, Altium has problems reporting accurate trace lengths when the routes are not cleanly connected from point to point.

Yes, Altium has issues when the routes have overlapping tracks, this includes tear drops.

Yes, Altium should create smarter net length measurement algorithms.

However:

If you don't apply teardrops, if you have no overlapping tracks, and you make clean connections you can get good results using Altium for High-speed designs.

Using the Transparent 2D view mode will allow you to see the bad connections.

The 'Fix Connections' script simplifies finding bad connections.

Thank you Petar ! ! !