Ghost Tracks

Fix:

Ctrl + B (select everything on the board)

Ctrl + X Cut (delete everything on the board)

Press E key then A key for Paste special.

Select Keep net name

Ghost Busted

Notes: I also received a tip to try Tools > Reset Error Markers (untested).

That's It !

Monday, January 25, 2016

Friday, January 15, 2016

Solder Robbers

Altium's 3D board view is an excellent tool for identifying the root cause of soldering related problems.

Example:

The x-ray below shows a pad that has insufficient solder (see mouse pointer).

Lets look at this using Altium's 3D design viewer.

Right away I see a solder robber. A trace was routed along side a pad, which created a larger area for the solder to flow across.

Fix:

That's It !

Example:

The x-ray below shows a pad that has insufficient solder (see mouse pointer).

Lets look at this using Altium's 3D design viewer.

Right away I see a solder robber. A trace was routed along side a pad, which created a larger area for the solder to flow across.

Fix:

That's It !

Thursday, January 14, 2016

Hole to Hole Clearance Rules

AD16 has options to use Drill Pairs for hole to hole clearances.

Click on images to view

In AD16.0.6 the drill pair rules are not working properly. Hole to Hole Clearance violations are not properly reported.

Also there are backward compatibility issues with using the drill pairs in AD16, they are not recognized in earlier versions of Altium.

When the DRC check is run in an earlier version you will get this error message.

Select Cancel.

Workaround for hole to hole clearance checks.

The solution shown below works and is backward and forward compatible.

Example 1: The rule shown below will catch both same net and different net hole to hole violations for holes greater than or equal to 6 mils in diameter.

(AsMils(HoleDiameter) >= 6)

Example 3: Via to Via Clearance Rule,

The edge of hole to edge of hole distance will be determined by the clearance rule and the annular ring sizes of the adjacent vias.

For 8/18 vias use 5mil via to via clearances to create Hole to Hole 15mil clearances.

Any Net was selected to apply the rule to both same and different nets.

That's It !

Click on images to view

In AD16.0.6 the drill pair rules are not working properly. Hole to Hole Clearance violations are not properly reported.

Also there are backward compatibility issues with using the drill pairs in AD16, they are not recognized in earlier versions of Altium.

When the DRC check is run in an earlier version you will get this error message.

Select Cancel.

Workaround for hole to hole clearance checks.

The solution shown below works and is backward and forward compatible.

Example 1: The rule shown below will catch both same net and different net hole to hole violations for holes greater than or equal to 6 mils in diameter.

(AsMils(HoleDiameter) >= 6)

Example 2: The rule shown below will catch both same net and different net hole to hole violations for any hole less than 6 mil in diameter.

(AsMils(HoleDiameter) < 6)

(AsMils(HoleDiameter) < 6)

Example 3: Via to Via Clearance Rule,

The edge of hole to edge of hole distance will be determined by the clearance rule and the annular ring sizes of the adjacent vias.

For 8/18 vias use 5mil via to via clearances to create Hole to Hole 15mil clearances.

Any Net was selected to apply the rule to both same and different nets.

That's It !

Thursday, January 7, 2016

PADS to Altium - Import Wizard

It's been awhile since I last used the PADS Import Wizard in Altium.

I imported a PADs ASCII V5 file using AD16.0.6

Poured the polygons and ran the DRC checks.

I ran into a few issues (500+). As expected, imports rarely go smoothly in any CAD tool.

The good news is that the majority of the DRCs are related to silkscreen and soldermask violations which can easily be fixed.

The vias came in un-tented (no soldermask) and caused a some DRC violations for soldermask to soldermask clearances. An easy to fix problem.

Fix: Tent VIAs.

For now, I will disable the batch mode for Manufacturing Rules (silkscreen and soldermask).

I'm more interested in the copper to copper violations.

Ignoring the Manufacturing Rules, I'm looking at a measly 154 violations.

Many of these violations are nonsensical same net violations.

For Example:

Same Net Only check for Via and Surface Mount Pad.

There are numerous instances in the design were GND VIAS are in direct contact with PADs that also have GND Nets. So this rule is obviously bogus.

Another bogus rule was: Same Net Via to Via.

Another bogus rule: Max length of a routed net.

Fix: Delete Bogus Rules

On layer 2 of this 4 layer board there are lot GND VIAs with tracks routed from GND VIA to GND VIA.

That's little interesting considering the same layer is also flooded with a GND polygon pour.

Same Layer (L2) with the polygons poured reveals the via to via tracks on layer 2 are not actually needed.

If left in the design these useless tracks will end up in the Gerber data.

Fix: Delete the useless GND tracks on Layer flooded with copper.

Note these GND tracks on layer 2 may have been in the original PADs data. When time permits I plan to review the design in PADs to better understand the source of these anomalies.

An interesting violation occurred where a copper region was found under a QFN.

click on image to view

Close up look

Six signal vias are shorted to solid copper (keepout) region under a QFN package.

The Region came in with different nets making contact with the Region.

Regions are dumb copper objects, unlike polygons which are smart copper.

The pink border and the checked Keepout box provided some insight for the purpose of the region.

This keepout should have came in as polygon cutout, vice a solid region.

Fix: Change the top layer keepout region to a top layer polygon cutout.

Select the Region > Right click > Properties > Change Kind to Polygon Cutout.

Pour the polygons and check the copper area under the QFN.

Fixing the keep out under the QFN resolved 115 of the 154 violations.

Only 2 warnings and 7 violations left, disregarding the silkscreen and soldermask.

I was making good progress cleaning up the the DRC violations, when AD16.0.6 suddenly closed and all of my work was lost. (nothing in the history folder)

It should be easier the second time around, since finding the problems and coming up with solutions is more than half of the battle.

Here we go again . . . practice makes perfect :-)

I opened up the *.pcbDoc which the Import Wizard generated and started working my way back through the fixes for the second time.

This time I'll remember to save the *.PcbDoc often, like after every fix that is implemented.

After applying all of the fixes shown above and saving my work :) I'm ready to knock out those last 2 warnings and 7 copper violations.

The last 7 violations

Region to PAD and Region to Track Clearance Violations

This gold finger edge connector has pads with copper to copper clearances of 9.252mil.

So, the 18mil clearance rule for Region to SMD Pad is not logical. And the 18mil Region to Track rule is not logical.

Fix: Modify Clearances Rules for Region to SMT Pad and Track.

The last 3 violations are due to the pads of a footprint being to close to a keepout that follows the board outline.

An RF End Launch SMA (J1) was placed close to the board edge and keepout.

It is not uncommon to find this violation in RF designs, because RF engineers don't won't to have a discontinuity in the RF path at the board edge.

Fabricators will point out that bare copper will be exposed on the board edge after routing the boards from the panel.

Fabricators typically request that the customer wavier the exposed copper or recommend that the copper be pulled back at least 10 mils from the board edge.

I could not find a rule to use to create an exception for this DRC.

Workarounds are need to resolve this DRC.

One option is the edit the keep out track as shown below.

Or it can be fixed using board clearance for the pullback in place of the keep out trace.

Note the Board Outline Clearance rule was introduced in AD15.

You can use both or either of these fixes in AD15 and higher.

To maintain backward compatibility with older versions of Altium edit the keepout track.

There were two warnings related to Non Plated Through Holes (NPTH).

At the lower and upper left corners of the board there were SMT pads that should have been interpreted as Non Plated Through Holes.

Looking at the pad properties

There were conflicting properties in the imported pad. Top layer and a drilled hole size of 55.118mil.

Fix : Change Layer From Top to Multi-Layer and re-pour the polygons.

The design is now DRC clean except for silkscreen and soldermask, which can easily be fixed.

Summary:

Porting designs between CAD tools always involves fixing a few problems.

Actually it was kinda fun, I like to solve problems.

Every CAD tool I have used occasionally crashes. Altium was able to reproduce and fix the crash that occurred after running DRC checks in this imported design.

Altium is diligently working to reduce crashes and improve stability.

That's It !

I imported a PADs ASCII V5 file using AD16.0.6

Poured the polygons and ran the DRC checks.

I ran into a few issues (500+). As expected, imports rarely go smoothly in any CAD tool.

The good news is that the majority of the DRCs are related to silkscreen and soldermask violations which can easily be fixed.

The vias came in un-tented (no soldermask) and caused a some DRC violations for soldermask to soldermask clearances. An easy to fix problem.

Fix: Tent VIAs.

For now, I will disable the batch mode for Manufacturing Rules (silkscreen and soldermask).

I'm more interested in the copper to copper violations.

Ignoring the Manufacturing Rules, I'm looking at a measly 154 violations.

Many of these violations are nonsensical same net violations.

For Example:

Same Net Only check for Via and Surface Mount Pad.

There are numerous instances in the design were GND VIAS are in direct contact with PADs that also have GND Nets. So this rule is obviously bogus.

Another bogus rule was: Same Net Via to Via.

Another bogus rule: Max length of a routed net.

Fix: Delete Bogus Rules

On layer 2 of this 4 layer board there are lot GND VIAs with tracks routed from GND VIA to GND VIA.

That's little interesting considering the same layer is also flooded with a GND polygon pour.

Same Layer (L2) with the polygons poured reveals the via to via tracks on layer 2 are not actually needed.

If left in the design these useless tracks will end up in the Gerber data.

Fix: Delete the useless GND tracks on Layer flooded with copper.

Note these GND tracks on layer 2 may have been in the original PADs data. When time permits I plan to review the design in PADs to better understand the source of these anomalies.

An interesting violation occurred where a copper region was found under a QFN.

click on image to view

Close up look

Six signal vias are shorted to solid copper (keepout) region under a QFN package.

The Region came in with different nets making contact with the Region.

Regions are dumb copper objects, unlike polygons which are smart copper.

The pink border and the checked Keepout box provided some insight for the purpose of the region.

This keepout should have came in as polygon cutout, vice a solid region.

Fix: Change the top layer keepout region to a top layer polygon cutout.

Select the Region > Right click > Properties > Change Kind to Polygon Cutout.

Pour the polygons and check the copper area under the QFN.

Fixing the keep out under the QFN resolved 115 of the 154 violations.

Only 2 warnings and 7 violations left, disregarding the silkscreen and soldermask.

I was making good progress cleaning up the the DRC violations, when AD16.0.6 suddenly closed and all of my work was lost. (nothing in the history folder)

It should be easier the second time around, since finding the problems and coming up with solutions is more than half of the battle.

Here we go again . . . practice makes perfect :-)

I opened up the *.pcbDoc which the Import Wizard generated and started working my way back through the fixes for the second time.

This time I'll remember to save the *.PcbDoc often, like after every fix that is implemented.

After applying all of the fixes shown above and saving my work :) I'm ready to knock out those last 2 warnings and 7 copper violations.

The last 7 violations

Region to PAD and Region to Track Clearance Violations

This gold finger edge connector has pads with copper to copper clearances of 9.252mil.

So, the 18mil clearance rule for Region to SMD Pad is not logical. And the 18mil Region to Track rule is not logical.

Fix: Modify Clearances Rules for Region to SMT Pad and Track.

The last 3 violations are due to the pads of a footprint being to close to a keepout that follows the board outline.

An RF End Launch SMA (J1) was placed close to the board edge and keepout.

It is not uncommon to find this violation in RF designs, because RF engineers don't won't to have a discontinuity in the RF path at the board edge.

Fabricators will point out that bare copper will be exposed on the board edge after routing the boards from the panel.

Fabricators typically request that the customer wavier the exposed copper or recommend that the copper be pulled back at least 10 mils from the board edge.

I could not find a rule to use to create an exception for this DRC.

Workarounds are need to resolve this DRC.

One option is the edit the keep out track as shown below.

Or it can be fixed using board clearance for the pullback in place of the keep out trace.

Note the Board Outline Clearance rule was introduced in AD15.

You can use both or either of these fixes in AD15 and higher.

To maintain backward compatibility with older versions of Altium edit the keepout track.

There were two warnings related to Non Plated Through Holes (NPTH).

At the lower and upper left corners of the board there were SMT pads that should have been interpreted as Non Plated Through Holes.

Looking at the pad properties

There were conflicting properties in the imported pad. Top layer and a drilled hole size of 55.118mil.

Fix : Change Layer From Top to Multi-Layer and re-pour the polygons.

The design is now DRC clean except for silkscreen and soldermask, which can easily be fixed.

Summary:

Porting designs between CAD tools always involves fixing a few problems.

Actually it was kinda fun, I like to solve problems.

Every CAD tool I have used occasionally crashes. Altium was able to reproduce and fix the crash that occurred after running DRC checks in this imported design.

Altium is diligently working to reduce crashes and improve stability.

That's It !

Sunday, January 3, 2016

AD14.3.20 to AD16.0.6

Comparing AD14.3.20 with AD16.0.6

When new versions of Altium Designer are released I use existing designs for testing.

I run DRC checks to see if anything is being reported that was not reported for designs released using older versions of Altium Designer.

I'm looking for backward or forward compatibility issues.

Using complex designs like Robert Feranec's iMX6 Rex is great for testing newer releases.

iMX6 Rex is an open source design. Using an open source design gives all interested parties an opportunity to download the project and compare test results.

Ok, let's get on with the test.

Then the same board file was tested in AD16.0.6.

One DRC violation was found in AD16 that was not in AD14.

The DRC is for a Diff Pair with matched length requirement of +/-0.127mm.

I took a quick look using the heads up display data.

click on image to view

According to the length data in the heads up display

CLK1_C_N = 18.431mm

CLK1_C_P = 18.425mm

And the rule was for matched lengths +/- 0.127mm.

Odd, the trace lengths appear to well matched in length ?

Check the rule, all looks normal here.

Let's do some more digging . . .

In AD16 open the PCB panel and select the Differential Pair Editor > DIFF100 > CLK_C

Now we can see the source of the DRC.

In AD16 we have Signal Length Data and Routed length Data.

Signal Length data was introduced in AD15 to support xSignals.

Signal length data is more accurate than Routed Length data. Signal length data is the shortest electrical distance from the center of one pin to the center of another pin.

Routed Length data includes all trace segments within a net. The Routed Length data includes trace segments that may not be following the shortest path between two points.

iMX6 Rex was originally designed using AD13 and later updated to AD14.

In AD15.1.15 the design will also pass all DRC checks.

AD15.1.15 and earlier versions do not include Signal Length data.

PCB Panel > From To Editor:

CLK1_C_N

CLK1_C_P

CLK1_C_N = 18.10653mm

CLK1_C_P = 18.11329mm

The From To Editor length data is also within the 0.127mm tolerance.

Summary:

Heads up Net Length

CLK1_C_N = 18.431mm

CLK1_C_P = 18.425mm

From To Editor Net Length

CLK1_C_N = 18.11329mm

CLK1_C_P = 18.10653mm

xSignal Length

CLK1_C_N = 18.42463mm

CLK1_C_P = 18.06434mm

AD16 uses xSignal length data for DRC checks, which is more accurate than routed length data.

When accuracy is needed, use Signal Length.

Users should not rely on Routed length data for matching trace lengths.

Users should not rely on From To Editor data for matching trace lengths.

For a more consistent user experience Altium could update the From To Editor to use the more accurate xSignal data lengths.

That's It !

Friday, January 1, 2016

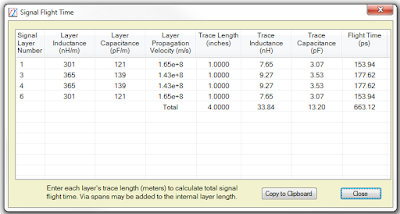

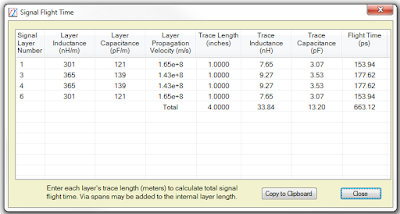

Propagation Delay - ICD Stackup Planner

Example using ICD Stackup Planner to find Propagation Delay (Tpd).

Tpd is Transition Propagation Delay.

And velocity is the reciprocal of Tpd.

If Tpd = 139pS/inch then velocity = 1/139 = 0.00719 inches per pSec.

If Tpd = 170pS/inch then velocity = 1/170 = 0.00588 inches per pSec.

Rule of thumb: Typical FR4 material 6mils of trace is ~ 1 pSec.

Here is a 6 layer stackup designed by a popular fabricator which includes Tpd data.

click on images to view

Many fabricators do not include Tpd data in the stackup.

Using ICD's Stackup Planner you can easily calculate Tpd.

Import or create your stackup in ICD's Stackup Planner.

Then on the main menu select Signal Flight Time

As shown below enter 1 inch for each signal layer.

The signal Propagation Delay (Tpd) in pSec/inch for each layer will be displayed in the Flight Time column.

That's It !

Tpd is Transition Propagation Delay.

And velocity is the reciprocal of Tpd.

If Tpd = 139pS/inch then velocity = 1/139 = 0.00719 inches per pSec.

If Tpd = 170pS/inch then velocity = 1/170 = 0.00588 inches per pSec.

Rule of thumb: Typical FR4 material 6mils of trace is ~ 1 pSec.

Here is a 6 layer stackup designed by a popular fabricator which includes Tpd data.

click on images to view

Many fabricators do not include Tpd data in the stackup.

Using ICD's Stackup Planner you can easily calculate Tpd.

Import or create your stackup in ICD's Stackup Planner.

Then on the main menu select Signal Flight Time

As shown below enter 1 inch for each signal layer.

The signal Propagation Delay (Tpd) in pSec/inch for each layer will be displayed in the Flight Time column.

That's It !

Subscribe to:

Comments (Atom)