View Configuration > Right click > Add Component Layer Pair

Click on image to view

As shown above I prefer to display the Mechanical Layer numbers in my component layer pairs. This involves creating, then editing the pair and selecting N/A for the Layer Type.

That's it !

Sunday, December 23, 2018

Saturday, December 15, 2018

VbScript - Get Folder

The snippet of VB script can be used to fetch a folder's name.

' Get Target Folder Path

CONST MY_COMPUTER = &H11 ' Use &H00 to include Desktop

CONST WINDOW_HANDLE = 0 ' Always = 0

CONST OPTIONS = 1 ' Default = 1

CONST BIF_NONEWFOLDERBUTTON = &H200 ' Hide Create New Folder Button

Sub SelectTargetFolder (dummy)

Set objShell = CreateObject("Shell.Application")

Set objFolder = objShell.Namespace(MY_COMPUTER)

Set objFolderItem = objFolder.Self

strPath = objFolderItem.Path

' Start in Folder

strPath = "C:\temp"

Set objFolder = objShell.BrowseForFolder _

(WINDOW_HANDLE, "Select a Target Folder:", OPTIONS, strPath)

If objFolder Is Nothing Then

exit sub

End If

Set objFolderItem = objFolder.Self

objSourcePath = objFolderItem.Path

msgbox "Target Folder: " & objSourcePath,,"Target Folder"

end sub

' Get Target Folder Path

CONST MY_COMPUTER = &H11 ' Use &H00 to include Desktop

CONST WINDOW_HANDLE = 0 ' Always = 0

CONST OPTIONS = 1 ' Default = 1

CONST BIF_NONEWFOLDERBUTTON = &H200 ' Hide Create New Folder Button

Sub SelectTargetFolder (dummy)

Set objShell = CreateObject("Shell.Application")

Set objFolder = objShell.Namespace(MY_COMPUTER)

Set objFolderItem = objFolder.Self

strPath = objFolderItem.Path

' Start in Folder

strPath = "C:\temp"

Set objFolder = objShell.BrowseForFolder _

(WINDOW_HANDLE, "Select a Target Folder:", OPTIONS, strPath)

If objFolder Is Nothing Then

exit sub

End If

Set objFolderItem = objFolder.Self

objSourcePath = objFolderItem.Path

msgbox "Target Folder: " & objSourcePath,,"Target Folder"

end sub

Wednesday, October 24, 2018

Schematics - Page Setup for 11x17 (Tabloid) PDF files

Open Outjob File > Select Schematic > Right Click > Page Setup

Select Tabloid, Landscape, Color and Fit Document On Page

Select Preview

That's it !

Select Tabloid, Landscape, Color and Fit Document On Page

Select Preview

That's it !

Friday, August 24, 2018

Single Pin Nets - Outjob Report

The Single Pin Nets report can be found in the Outjob > Report Options . . .

click on image to view

That's it !

click on image to view

That's it !

Tuesday, July 24, 2018

Practical Design Constraints and Myths

Printed circuit board designs are constraint driven by customers and end use requirements.

Design Constraints Include:

Mechanical Constraints

Fabrication Costs

Assembly Costs

Design Time Costs

Time to Market

Proof of Concept Prototypes

Low / High Volume Production

Design for Manufacturing

Design for Test

Design for FCC or ETSI Compliance

Ease of Maintenance or Rework

Controlled Impedance Requirements

Signal Integrity

Power Distribution Networks

Thermal Considerations

Conducted and Radiated Emissions

Radiated Susceptibility

A plethora of design constraints are often heaped on designers. An overly constrained design can prove to be an exercise in futility for the PCB designer. Often times I see constraints that are not applicable or practical to apply to a specific design.

Designers often work with customers who have never actually designed anything more than a simple board. However the customers have either read an article or have been convinced by someone that some design practices are good and others are bad.

Designs are often overly constrained using what appears to be a cobbled together collection of best practices. Unfortunately a one size fits all set of rules and constraints does not apply well to PCB designs.

Let's consider a few designs that have widely varying end use requirements.

High-Speed Designs

RF Designs

Power Supplies

High Voltage Designs

Sensitive Analog Designs

Automotive and Medical Safety

Low Cost Commercial Designs

Industrial Grade Designs

Harsh Environment Designs

90 Degree Corners

Designers have been lead to believe that routes with square corners are a bad thing and they assume all square corners should be eliminated from a design.

I have some bad news for the no square corners camp. Every surface mount resistor placed on the board will introduce four sharp 90 degree turns in the signal path. I suggest they figure out how to design their boards without using resistors :)

Source: http://www.resistorguide.com/thin-and-thick-film/

45 Degree Corners for RF Designs

Regarding using arcs instead of 45 degree corners. After 20+ years of RF board design experience working mostly in the 2.4GHz and 5GHz I have concluded based on test results and experience that RF tracks with 45 degree corners are no worst than using smooth arcs.

At 10GHz or higher I would suggest using arcs vice 45 degree turns.

Related Links:

Source: Altium Blog

https://resources.altium.com/pcb-design-blog/pcb-routing-angle-myths-45-degree-angle-versus-90-degree-angle

click on image to view

Source: Eric Bogatin - Separating Myth From Reality in Signal Integrity.

Microsoft PowerPoint - Bogatin-Myths- MUG 2006-05-05.ppt [Compatibility Mode]

Also see: Douglas Brooks - http://www.ultracad.com/articles/90deg.pdf

More later . . .

Design Constraints Include:

Mechanical Constraints

Fabrication Costs

Assembly Costs

Design Time Costs

Time to Market

Proof of Concept Prototypes

Low / High Volume Production

Design for Manufacturing

Design for Test

Design for FCC or ETSI Compliance

Ease of Maintenance or Rework

Controlled Impedance Requirements

Signal Integrity

Power Distribution Networks

Thermal Considerations

Conducted and Radiated Emissions

Radiated Susceptibility

A plethora of design constraints are often heaped on designers. An overly constrained design can prove to be an exercise in futility for the PCB designer. Often times I see constraints that are not applicable or practical to apply to a specific design.

Designers often work with customers who have never actually designed anything more than a simple board. However the customers have either read an article or have been convinced by someone that some design practices are good and others are bad.

Designs are often overly constrained using what appears to be a cobbled together collection of best practices. Unfortunately a one size fits all set of rules and constraints does not apply well to PCB designs.

Let's consider a few designs that have widely varying end use requirements.

High-Speed Designs

RF Designs

Power Supplies

High Voltage Designs

Sensitive Analog Designs

Automotive and Medical Safety

Low Cost Commercial Designs

Industrial Grade Designs

Harsh Environment Designs

Myths still persist.

90 Degree Corners

Designers have been lead to believe that routes with square corners are a bad thing and they assume all square corners should be eliminated from a design.

I have some bad news for the no square corners camp. Every surface mount resistor placed on the board will introduce four sharp 90 degree turns in the signal path. I suggest they figure out how to design their boards without using resistors :)

Source: http://www.resistorguide.com/thin-and-thick-film/

45 Degree Corners for RF Designs

Regarding using arcs instead of 45 degree corners. After 20+ years of RF board design experience working mostly in the 2.4GHz and 5GHz I have concluded based on test results and experience that RF tracks with 45 degree corners are no worst than using smooth arcs.

At 10GHz or higher I would suggest using arcs vice 45 degree turns.

Related Links:

Source: Altium Blog

https://resources.altium.com/pcb-design-blog/pcb-routing-angle-myths-45-degree-angle-versus-90-degree-angle

click on image to view

Source: Eric Bogatin - Separating Myth From Reality in Signal Integrity.

Microsoft PowerPoint - Bogatin-Myths- MUG 2006-05-05.ppt [Compatibility Mode]

Also see: Douglas Brooks - http://www.ultracad.com/articles/90deg.pdf

More later . . .

Wednesday, July 18, 2018

Use Layer Color for Connection lines

In AD18 as shown below if your connection lines use layer colors, they can be hard to see.

Solution:

Disable (turn off) Use Layer Color for Connection lines

That's it !

Solution:

Disable (turn off) Use Layer Color for Connection lines

That's it !

Sunday, July 1, 2018

Split Planes - AD18.1.7 Gotcha

If you build a Split Plane with a No Net area on the plane that area will be flooded with copper assigned to GND.

3D View

2D View - Before Rebuilding Split Planes

2D View - After Rebuilding Split Planes

Tools > Split Planes > Rebuild . . .

Gerbers viewed in Camtasic (Negative Image)

(Negative Image) Black = Copper, Gray = No Copper

Tips:

Don't count on unused No Net areas to remain free of copper, they will default to GND.

Use Fills or Solid Regions assigned to No Net to remove copper.

That's it !

3D View

2D View - Before Rebuilding Split Planes

2D View - After Rebuilding Split Planes

Tools > Split Planes > Rebuild . . .

Gerbers viewed in Camtasic (Negative Image)

(Negative Image) Black = Copper, Gray = No Copper

Tips:

Don't count on unused No Net areas to remain free of copper, they will default to GND.

Use Fills or Solid Regions assigned to No Net to remove copper.

That's it !

Solder Paste Expansion for Not Fitted Parts

click on image to view

That's It !

(ObjectKind = 'Pad') And ((Component = 'C1') OR (Component = 'R10') OR (Component = 'R12'))

Or you can create a Component Class and set the Paste Expansion for the Class.

InComponentClass('DNP')

InComponentClass('DNP')

That's It !

Labels:

Not-Fitted,

PCB Rules,

PCB Rules Syntax,

Solder Paste

Thursday, May 3, 2018

Autorouting with Altium

Per Ben Jordan . . .

What 3rd Party Autorouters work with Altium?

As for 3rd party routers... SPECCTRA as mentioned yes, but also using the same transfer formats, Konekt ELECTRA and Eremex TOPOR work well. My pick of those would be TOPOR. But, depending on what your needs are, the built in Situs router can produce good results *if* you know how to use it, and *if* the design constraints are suitable. It won't do DDR or length tuning. The interactive ActiveRoute is what you want for those...

Found on LinkedIn: See Altium Designer Users Group

'via Blog this'

What 3rd Party Autorouters work with Altium?

As for 3rd party routers... SPECCTRA as mentioned yes, but also using the same transfer formats, Konekt ELECTRA and Eremex TOPOR work well. My pick of those would be TOPOR. But, depending on what your needs are, the built in Situs router can produce good results *if* you know how to use it, and *if* the design constraints are suitable. It won't do DDR or length tuning. The interactive ActiveRoute is what you want for those...

Found on LinkedIn: See Altium Designer Users Group

'via Blog this'

Thursday, April 26, 2018

Pin Swapping

Pin Swapping

Problem: Cannot be Swapped ?

Solution: Project Options > Options Tab > Allow for Pin Swapping

Pin Swap Methods:

Controlling How the Swaps are Performed on the Schematic

Notes:

Pins and tracks must NOT be fully routed or be connected (shorted) to other nets.

Problem: Cannot be Swapped ?

Solution: Project Options > Options Tab > Allow for Pin Swapping

Pin Swap Methods:

Controlling How the Swaps are Performed on the Schematic

In the PCB editor pin, pair and part swaps are performed by exchanging nets on component pads and corresponding copper. When the changes are merged into the schematics there are two ways that a pin swap can be handled, either by swapping the pins on the component symbol, or by swapping net labels on the wires attached to the pins. Each approach has its advantages and disadvantages.

Performing the swap on the schematic by swapping net labels can only be done if the connectivity is established through the net labels, that is, if the pins are not hard-wired together. The advantage of this approach is that the component symbol does not change, and can be updated from the library at a later date. This approach is the best choice for a complex component, such as an FPGA.

Notes:

Pins and tracks must NOT be fully routed or be connected (shorted) to other nets.

That's It !

Monday, April 2, 2018

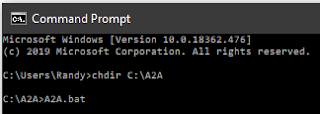

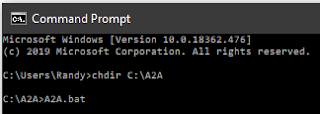

Allegro - Convert Binary to ASCII

REM Convert Allegro Binary to Allegro ASCII (*.brd to *.alg)

REM Place *.brd file, Allegro2Altium.bat and AllegroExportViews.txt in C:\A2A

REM Run the A2A.bat file in the C:\A2A folder on a PC with Allegro Installed

REM Open a Command Prompt > chdir C:\A2A

REM Enter: A2A.bat

REM For large designs the process can take several minutes.

REM You can minimize the Command window to the Task Bar.

REM Do not close the Command Window until the conversion is finished.

ECHO on

Allegro2Altium "*.brd"

REM Place *.brd file, Allegro2Altium.bat and AllegroExportViews.txt in C:\A2A

REM Run the A2A.bat file in the C:\A2A folder on a PC with Allegro Installed

REM Open a Command Prompt > chdir C:\A2A

REM Enter: A2A.bat

REM For large designs the process can take several minutes.

REM You can minimize the Command window to the Task Bar.

REM Do not close the Command Window until the conversion is finished.

ECHO on

Allegro2Altium "*.brd"

REM If needed rename AllegroASCII.txt to AllegroASCII.alg

REM end of A2A.bat file

click on images to view

Notes:

Allegro2Altium.bat and AllegroExportViews.txt can be found at:

"C:\Program Files\Altium\ADxx\System\AllegroExportViews.txt"

"C:\Program Files\Altium\ADxx\System\Allegro2Altium.bat"

Refer to: Allegro Import | Online Documentation for Altium Products

Tips:

When using the Import Wizard, there will be several forms that open to allow you to select the file(s) you are converting. In the case of the Allegro files, the first form will accept the Design (*.BRD or *.ALG) files, the second form will import Constraints files and the third form will import the footprint (*.DRA) files.

During the import process, if you are only interested in importing the *.DRA files, skip past the first two forms and then only import the footprint files.

That's it !

Notes:

Allegro2Altium.bat and AllegroExportViews.txt can be found at:

"C:\Program Files\Altium\ADxx\System\AllegroExportViews.txt"

"C:\Program Files\Altium\ADxx\System\Allegro2Altium.bat"

Refer to: Allegro Import | Online Documentation for Altium Products

Tips:

When using the Import Wizard, there will be several forms that open to allow you to select the file(s) you are converting. In the case of the Allegro files, the first form will accept the Design (*.BRD or *.ALG) files, the second form will import Constraints files and the third form will import the footprint (*.DRA) files.

During the import process, if you are only interested in importing the *.DRA files, skip past the first two forms and then only import the footprint files.

Related:

Extracta.exe

The PC with Cadence OrCAD / Allegro installed must have a System Environment Variable named Path that points the Installation folder tools\bin where extracta.exe is installed.

Control Panel > System > Advanced System Settings . . .

Example - System Environment Path Variable for OrCAD X

That's it !

Thursday, March 8, 2018

Port Cross References

My Preferred Port Cross References

Wednesday, February 28, 2018

NETS - Show Connections

To display Nets for selected Components

Click on image to view

Watch the Video:

Vote for Idea: #9095: AD18 - Show Selected Components Nets

Tip: View > Connections > Show . . .

Click on image to view

Watch the Video:

Vote for Idea: #9095: AD18 - Show Selected Components Nets

Tip: View > Connections > Show . . .

Thursday, January 25, 2018

Via-in-Pad Design Considerations

Printed Circuit Design & Fab Online Magazine - Via-in-Pad Design Considerations for Bottom Terminated Components on PCB Assemblies:

click on image to view

'via Blog this'

click on image to view

'via Blog this'

AD18 Project Outputs

Project Options - Point the Output Path to the Project Folder

Example: Project Outputs for 510-0105-xx_Rhino2

Add Section

Select Options

Check Custom Docs - Old Style . . .

Check Include Custom Data - Project Outputs and Rename to Project Outputs

Save Project File and Commit to SVN if the Project is under Version Control (SVN)

Select Prepare

And Wait for it . . .

Example: Project Outputs for 510-0105-xx_Rhino2

Add Section

Select Options

Check Custom Docs - Old Style . . .

Check Include Custom Data - Project Outputs and Rename to Project Outputs

Save Project File and Commit to SVN if the Project is under Version Control (SVN)

Select Prepare

And Wait for it . . .

Subscribe to:

Comments (Atom)

%20Beta%20Features%20Enabled.png)